オペアンプには、内部のBJTの特性が完全には揃わない等の理由で、オフセット電圧が発生してしまう。

LM324のオフセット電圧を、様々な角度から求めてみる。

図1-1:

オフセット電圧をDCゲイン倍(100dB)倍して3.32Vなので、

3.32/100000 = 33.2μV

出力が振り切れる恐れがあるので、このやり方は好ましくない。

【図1-1】

図1-2:

オフセット電圧に追従して、33.65μV

【図1-2】

図1-3:

バーチャルショートがかかっている状態で、本来V(-)= 0だが、

V(-)=33.6μV

と出ている。

【図1-3】

図1-4:

オペアンプのオフセット電圧は、数十μVと小さいことが多いので、DCゲインを上げて精度を上げる。図の例では、ノイズゲインを1000倍する。

Vout = 33.7mVと出ているので、33.7μV。

【図1-4】

■同相電圧範囲、電源電圧を超えた時の異常動作

同相電圧範囲、電源電圧を超えた電圧を印加すると、出力が反転することがある。

そのメカニズムは以下の通りである。

図2-1は、LM324の等価回路と、LM324を反転アンプとして使った例である。

細かくて見えないので、拡大図は、

http://kie.nu/1IJ4 ・・・・①

を参照ください。

【図2-1】

図①において、T5のベースが(-)入力端子で、T6のベースが(+)入力端子である。

今、(-)入力端子をGNDにし、(+)入力端子に0Vから下がっていく電圧を印加する。

(図2-2)

すると、図2-3に示すように、

マイナス電源-0.6V付近で、反転しプラスに張り付いてしまっていることが分かる。

【図2-2】

【図2-3】

なぜ、こうなるか。

図①において、(+)の電圧を下げていくと、T9のコレクタ電位も下がっていく。

すなわち、初段のVoutが下がっていくのである。

まず、(+)がGND以下でVeeより大きい時は、T1、T2、T8、T9が死ぬので、電流は以下のように流れている。

【図2-4】

この方向をプラスとしておく。

そして、-Vee-0.6V付近になったとき、T3のエミッタ電圧が-Veeになってしまい、T3とT9が死ぬ。

すると、初段のVoutは-Vee、電流(T3とT9のコレクタ)は今度はマイナスになる。

V+がVee-0.6V以下のとき、T3のベースはVee以下になるので、電流が逆転するのである。T7のベースはVee+0.6Vだから、T3のVceは負になる。コレクターベースは順バイアスされるので、電流は逆転するのである。

【図2-5】

電流が後段にいかないので、Q9がOFFになり、従って出力はプラスに張り付くという見方もできる。

■出力抵抗

残念ながらオペアンプは、純正のA*Viアンプではなく、直列に入る形の出力抵抗を持っている。

その出力抵抗がもたらす影響と問題点については、以下の知恵ノートを参照ください。

http://note.chiebukuro.yahoo.co.jp/detail/n177470

http://note.chiebukuro.yahoo.co.jp/detail/n257384

■同相信号除去比(CMRR)

オペアンプは、差動抵抗はあまり大きくはないが、同相抵抗は非常に高いのでCMRR値はよいのではないかと予想される。

オペアンプの同相信号除去比は、どの程度優秀なのか調べてみる。

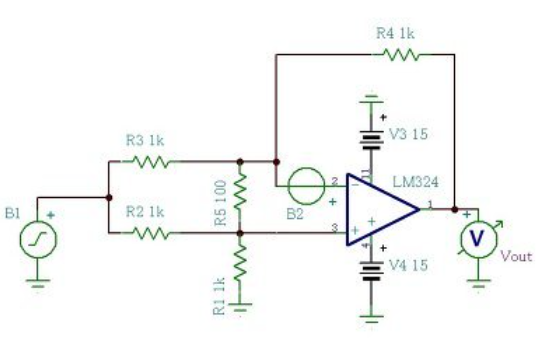

図3-1は、LM324のデータシートに載っていた、CMRR測定回路である。

オペアンプOPAMPの同相ゲイン観察回路

オペアンプOPAMPの同相ゲイン観察回路 - SonofSamlawのブログ (hatenablog.com)

【図3-1】

このモデルでは、同相電圧によるオフセット電圧が、図3-2のB2のようになって現れると考える。

【図3-2】

図3-3の(図3-2でR5がない)回路で同相電圧が生じてしまう原因として、

①抵抗の誤差によるもの

②図3-2のB2によるもの

が考えられる。そして、その割合は特定できない。

Vout = a*Vin + b*Vin

で、aは抵抗誤差、bは同相ゲインAcmによる係数であり、a、bは未知なのである。そこで、図3-3の回路で、Voutが0になるように、R1を調整する。-a ≒ bにするのである。

【図3-3】

今、この調整が完了したものと仮定する。

LM324の差動ゲインをAd、同相電圧をVcm、同相ゲインをAcmとすると、図3-3のブロック図は、図3-4のようになる。

OPAMPの+-端子間電圧はVoutによるNFにより、≒0になる。

しかし、+-端子の電圧はVinによって動く。これをVcmとする。このVcmからVoutまでのゲインをAcmとしてみる。実際はもっと複雑であり、比例関係にないのであるが、簡単にモデル化してみる。つまり、Vcm*AcmがVoutに加算されると考えるのである。

この加算点をゲインAdの前に持ってくると、Vcm*Acm/AdがOPAMP端子間の差動電圧に換算されて加算されたモデルになる。

これは、入オフセット電圧のVcmによる変化としてモデル化される。これが、図3-4である。

図3-3では、Vcm=Vin*R1/(R1+R2)となる。

【図3-4】

ここで、図3-2のように、R5を挟むことで、同相ゲインのみを上げるのである。

【図3-2再掲】

R5の効果を考える。

V(+)-V(-) = -(Vin*R4/(R3+R4) + Vout*R3/(R3+R4)) * R5/(R5 + R1//R2 + R3//R4)

V(+)-V(-) = Vin*R1/(R1+R2)*R5/(R5 + R1//R2 + R3//R4)

Vcm = Vin*R1/(R1+R2)

これを図3-4に入れると、R5の入ったブロック図となる。

上式を見ると、R5を入れたことにより、

K5 = R5/(R5 + R1//R2 + R3//R4)

Kcm = (R1/(R1 + R2))*(Acm/Ad)

とすると、

K1 → K1*K5

K2 → K2*K5

Kf → Kf*K5

となる。

Kcmはそのままである。

すると、Vcm(= Vin*R1/(R1+R2))からVoutまでのゲインのみが1/K5 倍になった事になる。

図3-2において、バーチャルショートが効いているから、電圧B2とおなじ電位差がR5に生じることになる。

R5を挟んだからといってB2が変わるわけではなく、R5両端の電位差は変わらないので、この観点から見ても、R5を挟んでもVcmは変わらないことが分かる。

つまり、R5を挟むことにより、

図3-4のK1、K2、Kfには、R5/(R5 + R1//R2 + R3//R4)が積算されるが、Vcmは変わらず、よって、Vcmのゲインのみが上がるように見える。

Vcmのゲインが、(R5 + R1//R2 + R3//R4)/R5に増えたように見えるのである。

R5を100Ω、R1 = R2 = R3 = R4 = 1kΩにしているから、

(R5 + R1//R2 + R3//R4)/R5 = (100 + 500 + 500)/100 = 11

で、Vcmのゲインのみが11倍となって現れる。

図3-3の測定で、抵抗誤差がないとすれば、

Vout = Vin*Kcm/Kf

= Vin*(R1/(R1+R2))*(Acm/Ad)/Kf

= Vin*(R1/(R1+R2))/(CMRR*Kf)

CMRR = (Vin/Vout)*(R1/(R1+R2))/Kf

Kf = R3/(R3+R4) = R2/(R1+R2)

であるから、

CMRR = (Vin/Vout)*(R1/R2)

一方、図3-2では、K1、K2、Kfが上記のように変わるので、、K1、K2に関わる分は変化がないので、 1/K5>>1で有るとすれば、R1の調整後、R5を入れた時、

Vout ≒ Vin*Kcm/(Kf*K5)

と近似できるので、

CMRR ≒ (Vin/Vout)*(R1/R2)/K5

よって、CMRR ≒ (Vin/Vout)*11

となり、

Vin/Vout = 64dB

であったから、11倍は20.8dBであるから、

64 + 20.8 = 85dB

で、データシートとぴったり結果が合うことが分かる。